Page 16 of 47

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 1:44 pm

by flynnsbit

On this build I get a "Keyboard error or locked" on the bios screen and any key including pulling up the mister menu gives multiple beeps like the actual keyboard buffer is stuck/full. using the Juko ST ver 2.30. Do I need to update that?

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 2:22 pm

by kitune-san

kitune-san wrote: ↑Sun Jun 26, 2022 9:10 am

Sorry. Still investigating. There may be other causes.

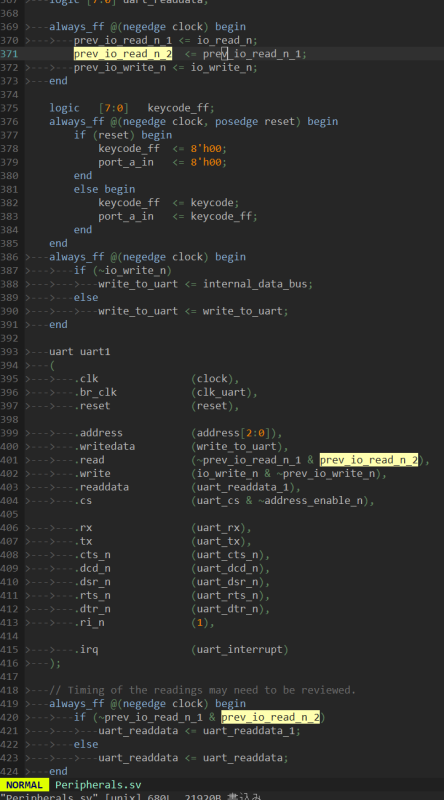

Apparently, if the output timing of read pulses to the uart module is delayed by one clock from the current timing, it will work fine during DMA transfers.

I am checking to see if the problem has really been resolved.

- 2022-06-26 231242.png (146.08 KiB) Viewed 3225 times

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 2:26 pm

by spark2k06

flynnsbit wrote: ↑Sun Jun 26, 2022 1:44 pm

On this build I get a "Keyboard error or locked" on the bios screen and any key including pulling up the mister menu gives multiple beeps like the actual keyboard buffer is stuck/full. using the Juko ST ver 2.30. Do I need to update that?

There has been no keyboard-related change from beta 1.0 to 1.1. Try restarting the core, see if it was a one-off...

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 2:32 pm

by flynnsbit

spark2k06 wrote: ↑Sun Jun 26, 2022 2:26 pm

flynnsbit wrote: ↑Sun Jun 26, 2022 1:44 pm

On this build I get a "Keyboard error or locked" on the bios screen and any key including pulling up the mister menu gives multiple beeps like the actual keyboard buffer is stuck/full. using the Juko ST ver 2.30. Do I need to update that?

There has been no keyboard-related change from beta 1.0 to 1.1. Try restarting the core, see if it was a one-off...

You're right, a completely cold boot (unplugged the mister) seems to have solved it. Sorry for the erroneous report. I am excited for the memory changes.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 3:43 pm

by spark2k06

suww37 wrote: ↑Sun Jun 26, 2022 1:35 pm

I tried to run PCXT beta 1.1 core, but as before, it failed to output from the lcd monitor connected to the vga port of the io board. Of course, the output to the HDMI port of the D-nano board works well. Perhaps my guess is that your lastest PCXT core doesn't allow individual settings in "mister.ini". Usually, individual settings for other cores of MiSTer are set by the sd card's core name(PCXT) in the "games" folder. Please check

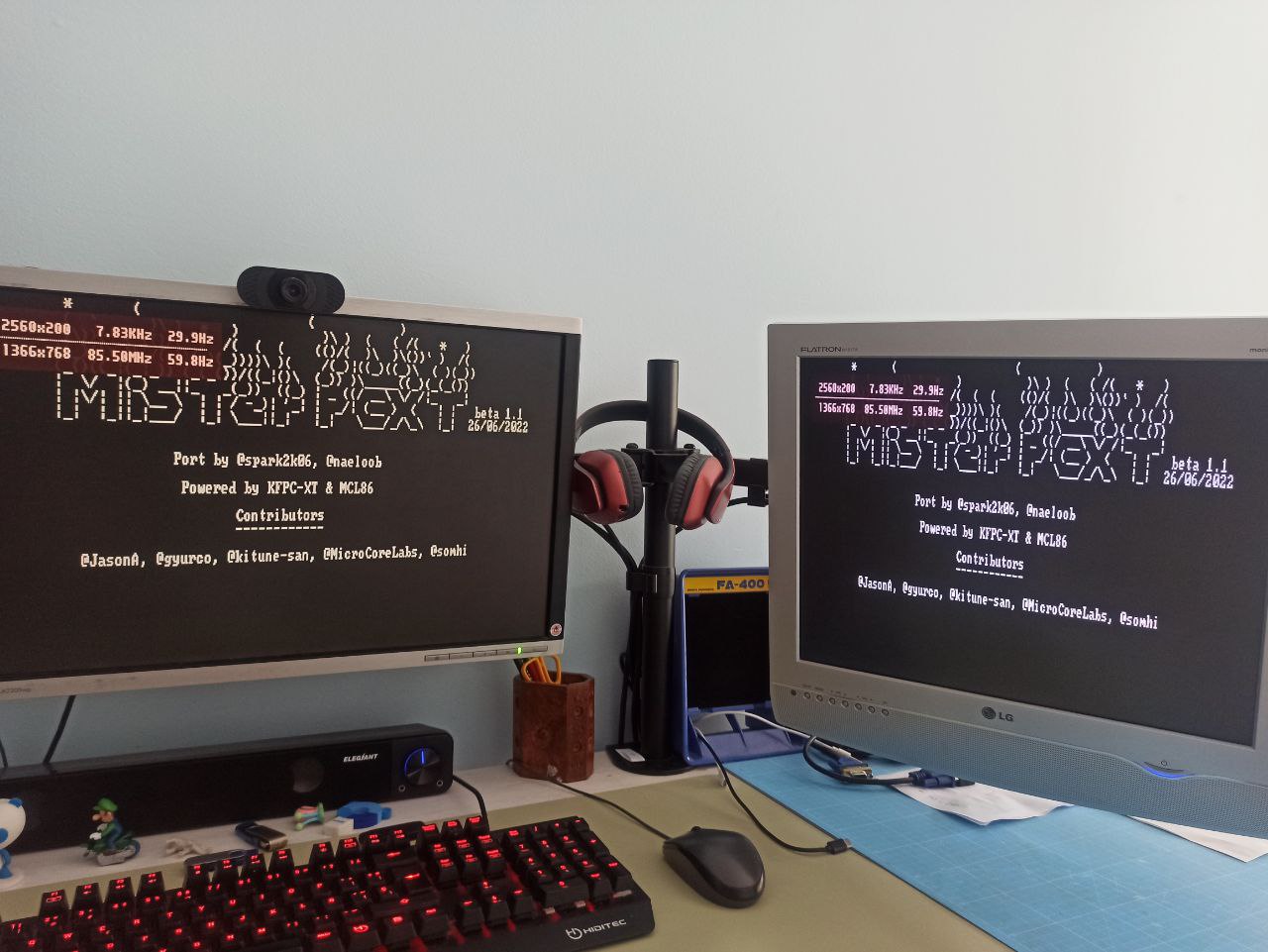

I have put the configuration you show in

MiSTer.ini and it works perfectly, both

HDMI and

VGA, look at the resolutions that the video module requires... maybe they are not compatible with your

LCD monitor?

- photo_2022-06-26_17-40-52.jpg (151.64 KiB) Viewed 3172 times

And once the splash screen is finished, in the

BIOS:

- photo_2022-06-26_17-45-08.jpg (113.58 KiB) Viewed 3167 times

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:07 pm

by breiztiger

same here keyboard doesn't work

cold boot doesn't seem to make the difference

edit : some time the core stuck at boot screen with only beep

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:07 pm

by spark2k06

Possibly, the Graphics Gremlin module needs some revision to return the frequency... especially the horizontal one, which comes out as very low, it is normal that not all monitors support it.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:09 pm

by spark2k06

breiztiger wrote: ↑Sun Jun 26, 2022 4:07 pm

same here keyboard doesn't work

cold reboot doesn't seem to make the difference

But I insist, in principle it should have nothing to do with the change from version

1.0 ->

1.1, no changes have been made to the keyboard.

If there are problems with the keyboard, they must be from before... they will be solved little by little, possibly with one of kitune-san latest changes, which I didn't get to include in the end. Let's give him time to take a good look at it, along with the

DMA issue, patience.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:11 pm

by NML32

My keyboard locks up randomly while playing Leisure Suit Larry 1.

I'm using PCXT v1.1 I haven't tried v1.0 or earlier versions.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:13 pm

by spark2k06

NML32 wrote: ↑Sun Jun 26, 2022 4:11 pm

My keyboard locks up randomly while playing Leisure Suit Larry 1.

I'm using PCXT v1.1 I haven't tried v1.0 or earlier versions.

Yes, and there are other games I have identified where the keyboard doesn't work:

Patience regarding the keyboard.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:13 pm

by Mills

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:31 pm

by kitune-san

The keyboard problem is caused by the lack of timing constraints.

If you are in a hurry,

It is incomplete, but please change the PCXT.sdc file as follows and give it a try:

Code: Select all

derive_pll_clocks

derive_clock_uncertainty

# core specific constraints

# Clocks

set CLK_CORE {emu|pll|pll_inst|altera_pll_i|cyclonev_pll|counter[0].output_counter|divclk}

set CLK_14_318 {emu|clk_14_318|q}

set CLK_4_77 {emu|clk_normal|clk_out|q}

set PCLK {emu|peripheral_clock|q}

create_generated_clock -name clk_14_318 -source [get_pins {emu|pll|pll_inst|altera_pll_i|cyclonev_pll|counter[1].output_counter|divclk}] -divide_by 2 [get_pins $CLK_14_318]

create_generated_clock -name clk_4_77 -source [get_pins $CLK_14_318] -divide_by 3 -duty_cycle 33 [get_pins $CLK_4_77]

create_generated_clock -name peripheral_clock -source [get_pins $CLK_4_77] -divide_by 2 [get_pins $PCLK]

create_generated_clock -name SDRAM_CLK -source { FPGA_CLK2_50 } [get_ports { SDRAM_CLK }]

# SDRAM

set_input_delay -clock { SDRAM_CLK } -max 6 [get_ports { SDRAM_DQ[*] }]

set_input_delay -clock { SDRAM_CLK } -min 3 [get_ports { SDRAM_DQ[*] }]

set_output_delay -clock { SDRAM_CLK } -max 2 [get_ports { SDRAM_DQ[*] SDRAM_DQM* SDRAM_A[*] SDRAM_n* SDRAM_BA SDRAM_CKE }]

set_output_delay -clock { SDRAM_CLK } -min 1.5 [get_ports { SDRAM_DQ[*] SDRAM_DQM* SDRAM_A[*] SDRAM_n* SDRAM_BA SDRAM_CKE }]

This requires a very long compile time.

Also, the two-stage F/F for device_clock and device_data in PCXT.sv is incomplete. Please correct the input to the chipset.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:52 pm

by suww37

spark2k06 wrote: ↑Sun Jun 26, 2022 3:43 pm

suww37 wrote: ↑Sun Jun 26, 2022 1:35 pm

I tried to run PCXT beta 1.1 core, but as before, it failed to output from the lcd monitor connected to the vga port of the io board. Of course, the output to the HDMI port of the D-nano board works well. Perhaps my guess is that your lastest PCXT core doesn't allow individual settings in "mister.ini". Usually, individual settings for other cores of MiSTer are set by the sd card's core name(PCXT) in the "games" folder. Please check

I have put the configuration you show in

MiSTer.ini and it works perfectly, both

HDMI and

VGA, look at the resolutions that the video module requires... maybe they are not compatible with your

LCD monitor?

photo_2022-06-26_17-40-52.jpg

And once the splash screen is finished, in the

BIOS:

photo_2022-06-26_17-45-08.jpg

Early on, your PCXT cores (PCXT_20220507.rbf, PCXT_20220510.rbf, PCXT_20220512.rbf) displayed good screen output through the 15pin vga port of the io board. The recently updated core (PCXT_20220523.rbf ~ PCXT_20220626.rbf) is not able to output screen . If I connect the hdmi port of the d-nano board to my lcd monitor, it outputs normally. Therefore, I think that there is no problem with the supported resolution of my lcd monitor. The monitor on the left in the picture I uploaded is a crt monitor that only pushes 15khz. It is connected to the d-nano board. If I set direct_video=0, the screen doesn't support 31khz, so the screen shakes and looks weird. I think that the LCD monitor connected to the io board connected at the same time should come out normally. Your early cores ( PCXT_20220507.rbf, PCXT_20220510.rbf, PCXT_20220512.rbf) were displayed normally. I can't understand why your latest cores don't support normal screen output in io board.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:53 pm

by spark2k06

kitune-san wrote: ↑Sun Jun 26, 2022 4:31 pm

The keyboard problem is caused by the lack of timing constraints.

If you are in a hurry,

It is incomplete, but please change the PCXT.sdc file as follows and give it a try:

Code: Select all

derive_pll_clocks

derive_clock_uncertainty

# core specific constraints

# Clocks

set CLK_CORE {emu|pll|pll_inst|altera_pll_i|cyclonev_pll|counter[0].output_counter|divclk}

set CLK_14_318 {emu|clk_14_318|q}

set CLK_4_77 {emu|clk_normal|clk_out|q}

set PCLK {emu|peripheral_clock|q}

create_generated_clock -name clk_14_318 -source [get_pins {emu|pll|pll_inst|altera_pll_i|cyclonev_pll|counter[1].output_counter|divclk}] -divide_by 2 [get_pins $CLK_14_318]

create_generated_clock -name clk_4_77 -source [get_pins $CLK_14_318] -divide_by 3 -duty_cycle 33 [get_pins $CLK_4_77]

create_generated_clock -name peripheral_clock -source [get_pins $CLK_4_77] -divide_by 2 [get_pins $PCLK]

create_generated_clock -name SDRAM_CLK -source { FPGA_CLK2_50 } [get_ports { SDRAM_CLK }]

# SDRAM

set_input_delay -clock { SDRAM_CLK } -max 6 [get_ports { SDRAM_DQ[*] }]

set_input_delay -clock { SDRAM_CLK } -min 3 [get_ports { SDRAM_DQ[*] }]

set_output_delay -clock { SDRAM_CLK } -max 2 [get_ports { SDRAM_DQ[*] SDRAM_DQM* SDRAM_A[*] SDRAM_n* SDRAM_BA SDRAM_CKE }]

set_output_delay -clock { SDRAM_CLK } -min 1.5 [get_ports { SDRAM_DQ[*] SDRAM_DQM* SDRAM_A[*] SDRAM_n* SDRAM_BA SDRAM_CKE }]

This requires a very long compile time.

Also, the two-stage F/F for device_clock and device_data in PCXT.sv is incomplete. Please correct the input to the chipset.

I have created a preliminary testing branch before the next beta, this time I add the proposal of @kitune-san... you can add that you comment, I don't know exactly how was the change or if I have to add it from a previous pull request that I rejected you, please feel free to make pull request to this branch, I accept it and generate a release for users to test it:

https://github.com/spark2k06/PCXT_MiSTe ... e_beta_1_2

Edit: I think I've made the two missing changes, I'll give it a try.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 4:58 pm

by spark2k06

suww37 wrote: ↑Sun Jun 26, 2022 4:52 pm

Early on, your PCXT cores (PCXT_20220507.rbf, PCXT_20220510.rbf, PCXT_20220512.rbf) displayed good screen output through the 15pin vga port of the io board. The recently updated core (PCXT_20220523.rbf ~ PCXT_20220626.rbf) is not able to output screen . If I connect the hdmi port of the d-nano board to my lcd monitor, it outputs normally. Therefore, I think that there is no problem with the supported resolution of my lcd monitor. The monitor on the left in the picture I uploaded is a crt monitor that only pushes 15khz. It is connected to the d-nano board. If I set direct_video=0, the screen doesn't support 31khz, so the screen shakes and looks weird. I think that the LCD monitor connected to the io board connected at the same time should come out normally. Your early cores ( PCXT_20220507.rbf, PCXT_20220510.rbf, PCXT_20220512.rbf) were displayed normally. I can't understand why your latest cores don't support normal screen output in io board.

Yes, very early on... honestly, I don't know how to fix this right now. If I ever find out anything, I'll let you know, thanks for your understanding

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 5:13 pm

by Mills

suww37 wrote: ↑Sun Jun 26, 2022 4:52 pm

spark2k06 wrote: ↑Sun Jun 26, 2022 3:43 pm

suww37 wrote: ↑Sun Jun 26, 2022 1:35 pm

I tried to run PCXT beta 1.1 core, but as before, it failed to output from the lcd monitor connected to the vga port of the io board. Of course, the output to the HDMI port of the D-nano board works well. Perhaps my guess is that your lastest PCXT core doesn't allow individual settings in "mister.ini". Usually, individual settings for other cores of MiSTer are set by the sd card's core name(PCXT) in the "games" folder. Please check

I have put the configuration you show in

MiSTer.ini and it works perfectly, both

HDMI and

VGA, look at the resolutions that the video module requires... maybe they are not compatible with your

LCD monitor?

photo_2022-06-26_17-40-52.jpg

And once the splash screen is finished, in the

BIOS:

photo_2022-06-26_17-45-08.jpg

Early on, your PCXT cores (PCXT_20220507.rbf, PCXT_20220510.rbf, PCXT_20220512.rbf) displayed good screen output through the 15pin vga port of the io board. The recently updated core (PCXT_20220523.rbf ~ PCXT_20220626.rbf) is not able to output screen . If I connect the hdmi port of the d-nano board to my lcd monitor, it outputs normally. Therefore, I think that there is no problem with the supported resolution of my lcd monitor. The monitor on the left in the picture I uploaded is a crt monitor that only pushes 15khz. It is connected to the d-nano board. If I set direct_video=0, the screen doesn't support 31khz, so the screen shakes and looks weird. I think that the LCD monitor connected to the io board connected at the same time should come out normally. Your early cores ( PCXT_20220507.rbf, PCXT_20220510.rbf, PCXT_20220512.rbf) were displayed normally. I can't understand why your latest cores don't support normal screen output in io board.

Did you try vsync_adjust=0 in mister.ini? It usually makes everything work (at least on lcd), at the cost of (maybe) choppy scrolls in any smooth scrolling game/program (very few for CGA). But for the moment It can be used to test. My lcd, connected using vga or dvi adapters, did not display the MDA graphics if vsync_adjust is not 0.

Also this is still a beta, bugs will be common for the moment.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 6:30 pm

by spark2k06

I have synthesised a preliminary version of the next beta with kitune-san's suggestions, for those who have problems with the keyboard, you can try it out:

https://github.com/spark2k06/PCXT_MiSTe ... REBETA.rbf

- pcxt_prebeta_01.png (6.99 KiB) Viewed 2993 times

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 6:45 pm

by MicroCoreLabs

I suggest making some clock domains asynchronous with each other using "set_clock_groups -asynchronous " in the .sdc file

Without this constraint Quartus will assume there is a phase relationship between all clock domains and will take much longer to Fit. I also suggest constraining the 100Mhz clock which the MCL86 uses if it is not already.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 7:01 pm

by breiztiger

sorry but doesn't fix keyboard problem for me ;-(

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 7:50 pm

by Mills

breiztiger wrote: ↑Sun Jun 26, 2022 7:01 pm

sorry but doesn't fix keyboard problem for me ;-(

Try another keyboard or unplug other things you might have (gamepads ect...), just in case.

Re: MiSTer PCXT

Posted: Sun Jun 26, 2022 7:56 pm

by NML32

No more keyboard lockups playing LSL1.

I recorded some gameplay in Color, Mono Amber, and Green.

https://youtu.be/oV1yH6auCrg

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 3:04 am

by kitune-san

Thanks for the suggestion.

The 100mhz clock is constrained by derive_pll_clocks because it is output from a PLL.

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 5:44 am

by spark2k06

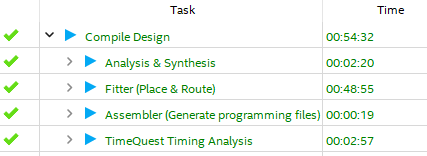

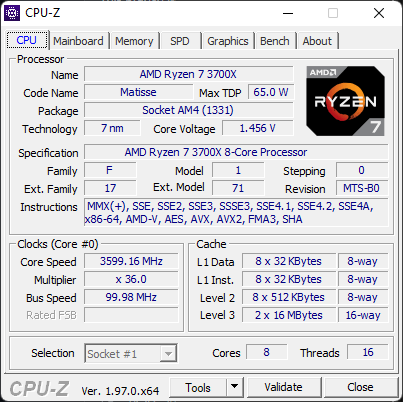

I don't understand much about these concepts, but following @MicroCoreLabs suggestion and following a bit the content of this documentation:

https://vlsi.pro/clock-groups-set_clock_groups/

In our case I think we could only separate the

SDRAM_CLK clock from the rest, which I understand must have the same phase:

Code: Select all

set_clock_groups -asynchronous -group {SDRAM_CLK} -group {clk_14_318 clk_4_77 peripheral_clock}

The gain in this case has not been better, quite the opposite:

- pcxt_prebeta_02.png (6.62 KiB) Viewed 2732 times

I upload it to the releases folder of the

pre_beta_1_2 branch... in case someone can confirm that the performance remains the same with this change:

https://github.com/spark2k06/PCXT_MiSTe ... 2/releases

As a side note, without these time constrains and with my

CPU, the fit time is 8 minutes... that's my

CPU:

- My_CPU.png (24.44 KiB) Viewed 2732 times

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 6:13 am

by MicroCoreLabs

set_clock_groups -asynchronous -group {SDRAM_CLK} -group {clk_14_318 clk_4_77 peripheral_clock}

I would check that all of your clocks are tagged as asynchronous of each other, that 100Mhz clock is included, and that the full module path of your clock names are correct.

An example might look like this:

set_clock_groups -asynchronous \

-group [get_clocks Top_level|Clocking_Core|Local_PLL|clk_100]\

-group [get_clocks Top_level|Clocking_Core|clk_14_318] \

-group [get_clocks Top_level|Clocking_Core|clk_4_77] \

-group [get_clocks Top_level|Clocking_Core|peripheral_clock] \

-group [get_clocks Top_level|SRAM_Core|SDRAM_CLK]

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 7:38 am

by breiztiger

sorry but on two mister config (home & work) no keyboard with prebeta2

1st mister with only 32mo sdram usb board logitech k400 sony ps3 bluetooth

2nd mister with 128mo sdram blisster microsoft wireless kit keyboard and mouse 8bit m30 2.4ghz

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 7:45 am

by spark2k06

breiztiger wrote: ↑Mon Jun 27, 2022 7:38 am

sorry but on two mister config (home & work) no keyboard with prebeta2

1st mister with only 32mo sdram usb board logitech k400 sony ps3 bluetooth

2nd mister with 128mo sdram blisster microsoft wireless kit keyboard and mouse 8bit m30 2.4ghz

- ENYFM575YVDEJACJE6IS3E6ZHU.jpg (64.16 KiB) Viewed 2435 times

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 9:01 am

by Mills

kitune-san wrote: ↑Sun Jun 26, 2022 4:31 pm

The keyboard problem is caused by the lack of timing constraints.

If you are in a hurry,

It is incomplete, but please change the PCXT.sdc file as follows and give it a try:

Code: Select all

derive_pll_clocks

derive_clock_uncertainty

# core specific constraints

# Clocks

set CLK_CORE {emu|pll|pll_inst|altera_pll_i|cyclonev_pll|counter[0].output_counter|divclk}

set CLK_14_318 {emu|clk_14_318|q}

set CLK_4_77 {emu|clk_normal|clk_out|q}

set PCLK {emu|peripheral_clock|q}

create_generated_clock -name clk_14_318 -source [get_pins {emu|pll|pll_inst|altera_pll_i|cyclonev_pll|counter[1].output_counter|divclk}] -divide_by 2 [get_pins $CLK_14_318]

create_generated_clock -name clk_4_77 -source [get_pins $CLK_14_318] -divide_by 3 -duty_cycle 33 [get_pins $CLK_4_77]

create_generated_clock -name peripheral_clock -source [get_pins $CLK_4_77] -divide_by 2 [get_pins $PCLK]

create_generated_clock -name SDRAM_CLK -source { FPGA_CLK2_50 } [get_ports { SDRAM_CLK }]

# SDRAM

set_input_delay -clock { SDRAM_CLK } -max 6 [get_ports { SDRAM_DQ[*] }]

set_input_delay -clock { SDRAM_CLK } -min 3 [get_ports { SDRAM_DQ[*] }]

set_output_delay -clock { SDRAM_CLK } -max 2 [get_ports { SDRAM_DQ[*] SDRAM_DQM* SDRAM_A[*] SDRAM_n* SDRAM_BA SDRAM_CKE }]

set_output_delay -clock { SDRAM_CLK } -min 1.5 [get_ports { SDRAM_DQ[*] SDRAM_DQM* SDRAM_A[*] SDRAM_n* SDRAM_BA SDRAM_CKE }]

This requires a very long compile time.

Also, the two-stage F/F for device_clock and device_data in PCXT.sv is incomplete. Please correct the input to the chipset.

The core is very stable with that, no more ram failures or read disk errors

. Sometimes it won't find the hard disk or keyboard, this is solved by resetting the mister.

breiztiger wrote: ↑Mon Jun 27, 2022 7:38 am

sorry but on two mister config (home & work) no keyboard with prebeta2

1st mister with only 32mo sdram usb board logitech k400 sony ps3 bluetooth

2nd mister with 128mo sdram blisster microsoft wireless kit keyboard and mouse 8bit m30 2.4ghz

I'm using a wireless keyboard and I have no keyboard if I select MDA output, maybe it is related. Also keyboard fails in some apps / games randomly, but I suppose it is normal for now... I'll try another non wireless keyboard and see if it works better.

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 9:29 am

by held

Quick question: can MiSTerFS from ao486 be easily ported to PCXT ?

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 9:49 am

by breiztiger

just try with only wired keyboard the same

as i have unstable mister i go back to official but the same ;-(

Re: MiSTer PCXT

Posted: Mon Jun 27, 2022 10:15 am

by wark91

did you try to rename your config directory to be sure to use the stock configuration on PCXT core ?